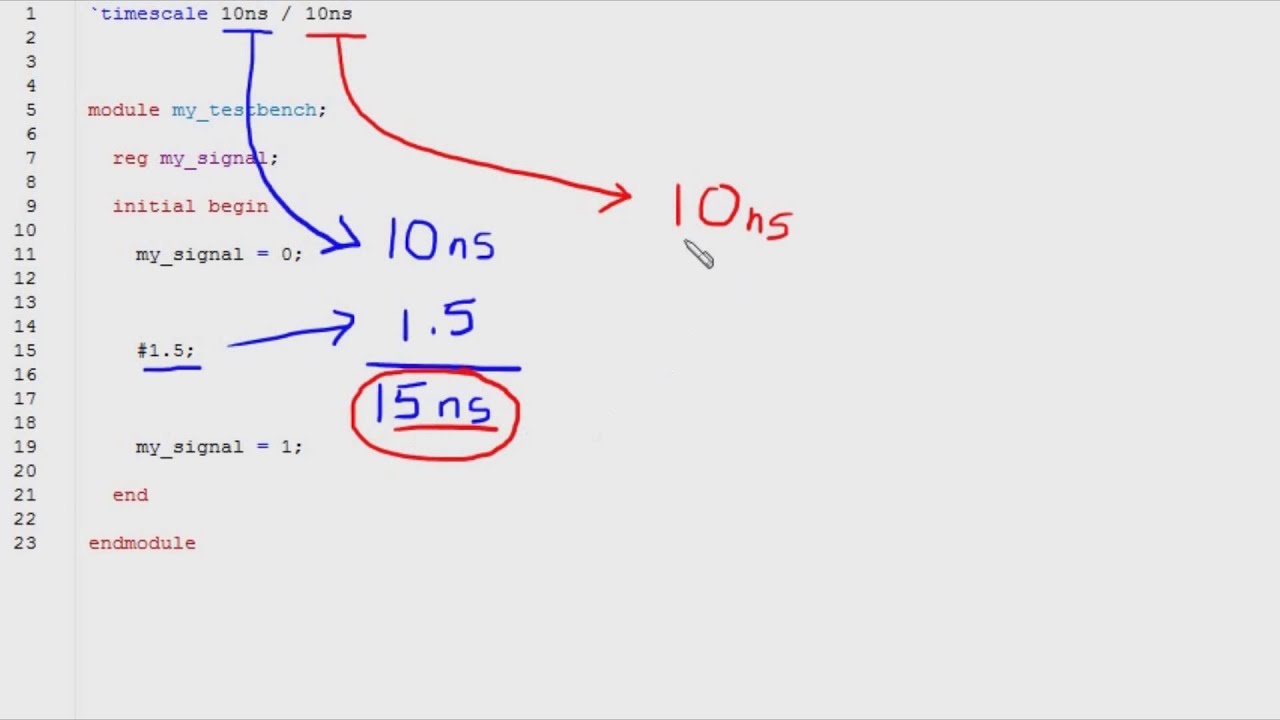

The Verilog Language and Application. The macro will be defined with a syntax define macroname textstring and usage syntax is macroname. Macro Definitions: It is used to define a text macro in Verilog. Timescale 1ns/100ps // time unit 1ns, precision 1/10ns. Example: timescale 1ns/1ps //unit 1ns, precision 1/1000ns. Syntax: timescale timeunit / timeprecision.

Logical Area and Logical Efficiency. Logical Effort.Predicting Delay. Junction Capacitance.Overlap Capacitance. Transistor Parasitic Capacitance.

Practical Issues.FPGAs in Use. EPROM and EEPROM Technology. Standard-Cell Design.Datapath-Cell Design.

ACT 2 and ACT 3 Logic Modules. Multiplexer Logic as FunctionGenerators. Shannones Expansion Theorem.

Metastability.Clock Input. Programmable ASIC I/O Cells. Power Dissipationin Complex PLDs. Xilinx CLB Analysis.Altera FLEX. Actel Logic Module Analysis.

Schematic Icons and Symbols. Hierarchical Design.The Cell Library. Programmable ASIC Design Software. ACT 2 andACT 3 Interconnect. Antifuse Parasitic Capacitance. RCDelay in Antifuse Connections.

Low-level Design Languages. Schematic-Entry Tools.Back-Annotation. Vectored Instances and Buses.Edit-in-Place.

Generics.Type Declaration. Other Packages.Creating Packages. Packages and Libraries.Standard Package. Syntax and Semantics of VHDL.Identifiers and Literals. CFI Connectivity Model.10.

Process Statement.Concurrent Procedure Call. Case Statement.Other Sequential Control Statements. Assertion and Report Statements.Assignment Statements. Predefined Attributes.Sequential Statements.

Procedures and Assignments.Continuous Assignment Statement. Basics of the Verilog Language. Configurations and Specifications. Generate Statement.Execution. ConcurrentAssertion Statement.

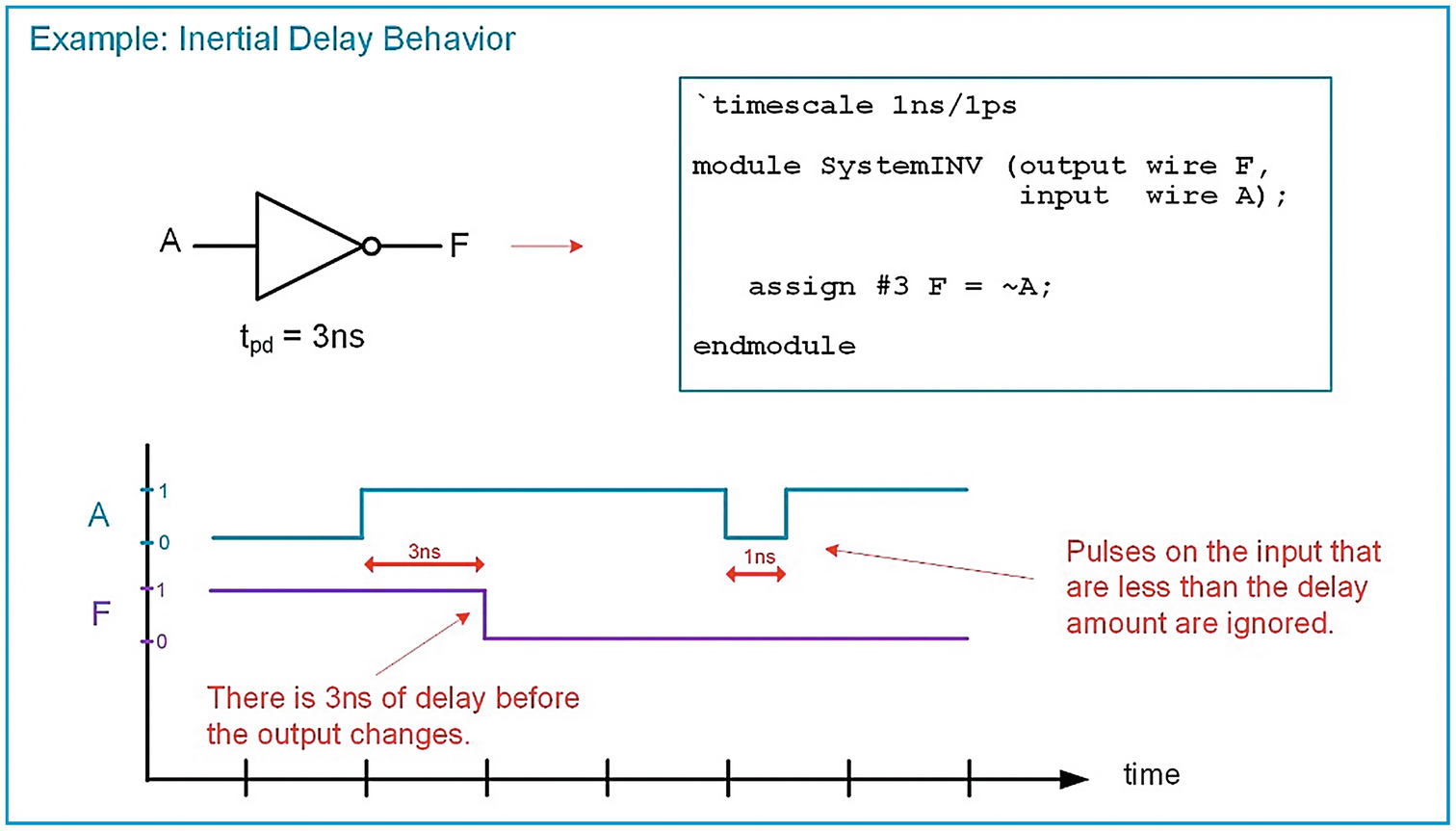

Stochastic Analysis Tasks. Timescale, Simulation,and Timing Check Tasks. Viterbi Encoder.The Received Signal. Net and Gate Delay.Pin-to-pin Delay. Procedural Continuous Assignment.Tasks and Functions. Wait Statement.Blocking and Non-blocking Assignments.

Synthesis of the ViterbiDecoder. Inside a Logic Synthesizer. An Actel Version of theComparator/MUX. Logic Synthesis.A Logic-Synthesis Example.

Shift Registers and Clocking in VHDL.Adders and Arithmetic Functions. Combinational Logic Synthesis in VHDL.Multiplexers in VHDL. VHDL and Logic Synthesis.Initialization and Reset. Datapath Synthesis in Verilog. Component Instantiationin Verilog. Sequential Logic in Verilog.

The Comparator/MUX Example.Structural Simulation. The Different Types of Simulation. Optimization of the Viterbi Decoder. The Engine Controller.Performance-Driven Synthesis. Messages During Synthesis. Memory Synthesis in Verilog.

The Importance of Test.Boundary-Scan Test. Transistor-Level Simulation.A PSpice Example. Adding an Assertion.Completing a Proof. Understanding Formal Verification. Limitations of Logic Simulation. Using a Library Data Book.

Fault Simulation in an ASICDesign Flow. A Fault Simulation Example. Fault-Simulator Logic Systems. Nondeterministic Fault Simulation.Fault-Simulation Results. Concurrent Fault Simulation.

Production Tester Vector Formats. How the Test Software Works. Controllability and Observability.Scan Test.

IterativePartitioning Improvement. Constructive Partitioning. ASimple Partitioning Example. AutomaticPartitioning with FPGAs. Subthresholdand Leakage Current. Estimating ASIC Size.Power Dissipation.

Placement Goals AndObjectives. Placement Terms and Definitions. Measurement of Delay in Floorplanning.Floorplanning Tools. Floorplanning.Floorplanning Goals and Objectives. Floorplanning and Placement. OtherPartitioning Objectives.

SDFfor Floorplanning and Placement. ASimple Placement Example. Timing-Driven Placement Methods. Iterative Placement Improvement.Placement Using Simulated Annealing. Eigenvalue Placement Example.

Detailed Routing.Goals and Objectives. Global Routing InsideFlexible Blocks. Global Routing Between Blocks.

Timing-Driven Detailed Routing. Constraints and Routing Graphs. Algorithms.Left-Edge Algorithm.

Mask Preparation.Appendix A.

0 kommentar(er)

0 kommentar(er)